FLIP FLOP

KLASIFIKASI RANGKAIAN DIGITAL

SIMBOL FLIP FLOP

SIMBOL JK FF

Flip-Flop (FF) adalah rangkaian digital

yang digunakan untuk menyimpan satu bit secara semi permanen sampai ada suatu

perintah untuk menghapus atau mengganti isi dari bit yang disimpan.

Dalam elektronika, Flip-Flop

adalah sebuah sirkuit yang memiliki dua keadaan stabil yang dapat digunakan

untuk menyimpan suatu keadaan informasi. Keadaan ini dapat diubah dengan

mengganti sinyal input dan akan menghasilkan satu atau dua output.

§Flip-Flop merupakan elemen terpenting penyusun memori.

§Flip-Flop (FF) merupakan gabungan beberapa gerbang dasar yang disusun sedemikian rupa sehingga mampu digunakan untuk menyimpan informasi.

§Bagaimana gerbang-gerbang tersebut saling terhubung tidak sama memunculkan beberapa jenis FF.

§Fungsi FF, selain untuk menyimpan bilangan biner adalah :

üMencacah pulsa

üMenyerempakkan/men-sinkron-kan

rangkaian aritmatika

§Flip-flop

bersifat Bistable : dua

kondisi stabil 0 atau 1. Kondisi ini akan tetap stabil/ tidak

akan berubah jika tidak ada pemicu (input) yang masuk.

§FF juga dikenal dengan istilah latch dan bistable multivibrator.

CLOCK

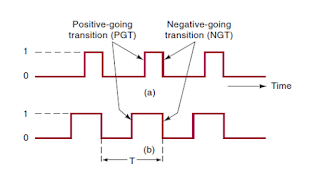

§Pada sistem digital sinkron, kapan perubahan output dapat terjadi ditentukan oleh sinyal yang disebut clock atau detak.

§Sinyal clock ini berupa gelombang kotak.

§Output sistem dapat berubah nilai pada saat sinyal clock mengalami perubahan (transisi), yaitu :

ØPerubahan dari 0 ke 1 (Positive-Going

Transition, PGT)

ØPerubahan dari 1 ke 0 (Negative-Going

Transition, NGT)

§Jadi Clocked FF adalah untai

Flip-Flop yang dilengkapi dengan sinyal clock.

PGT vs NGT

§Kecepatan suatu sisitem digital beroperasi ditentukan oleh periode sinyal clock-nya.

§Waktu yang diperlukan untuk menyelesaikan 1 siklus clock disebut periode (T).

Clocked-FF / FF terdetak

§Selain input kendali, terdapat input tambahan untuk clock

(CLK).

§Input kendali menentukan keluaran FF, sedangkan input

CLK menentukan kapan perubahan pada output

terjadi.

NAND GATE LATCH

§Dua masukkan dan dua

keluaran.

§Dua Inputan yaitu S =

set dan R = reset,

§Dua output yaitu Q

dan Q’ .Output Q dianggap merupakan output normal, dan dalam kondisi

normal kedua output selalu merupakan komplementer.

§Karena fungsi flip-flop

memegang data sementara, maka flip-flop ini sering disebut SR Latch Flip-Flop.

§Dibentuk dari kombinasi dua

gerbang NAND atau kombinasi dari dua gerbang NOR.

§IC yang dipakai untuk SR

flip-flop bisa IC 7400 (IC NAND) atau IC 7402 (IC NOR).

SR NAND LATCH

§SET=RESET=1; Tidak menyebabkan perubahan pada output

Q.

§SET=0 dan RESET=1; Mengakibatkan Q=1.

§SET=1 dan RESET=0; Menghasilkan Q=0.

SET=RESET

=0; Kondisi tak diinginkan.

SR NOR LATCH

§SET=RESET=0 ; Tidak menyebabkan perubahan pada output

Q.

§SET=1 dan RESET=0; Mengakibatkan Q=1.

§SET=0 dan RESET=1; Menghasilkan Q=0.

§SET=RESET =1 ; Kondisi tak diinginkan.

Gate/Clock

SR Flip Flop

JK FLIP FLOP (TERDETAK)

§Dianggap sebagai flip-flop

universal, karena flip-flop jenis lain dapat dibuat dari flip-flop JK.

§Simbol logika terbagi tiga

input sinkron (J, K dan CK). Input J dan K merupakan input data, dan input

clock memindahkan data dari input ke output.

§Diperlukan keseluruhan pulsa

(bukan sekedar tansisi low ke high atau high ke low saja) untuk memindahkan

data dari input ke output. IC yang digunakan dalam JK flip-flop adalah IC 7400.

§Dua sifat unik dari flip-flop JK adalah:

1. Jika kedua data input pada keadaan nol, tidak akan terjadi

perubahan pada output meskipun diberikan sinyal clock (output tetap).

2. Jika kedua data input pada keadaan satu, pada tiap pulsa clock

data output akan berubah dari sebelumnya (komplemen dari data sebelumnya).

§Kita dapat membangun suatu flip-flop JK

dari gerbang NAND. Nampak bahwa sebenarnya flip-flop JK terdiri dari dua

flip-flop yang terangkai menjadi satu

TIMING DIAGRAM JK FF (PGT)

MASTER SLAVE JK FF

§Terdiri dari dua buah

flip-flop, yaitu Master FF (MFF) dan Slave FF (SFF).

§Memiliki 3 buah terminal

input yaitu J, K dan Clock.

§IC yang bisa dipakai untuk menyusun JK FF

adalah tipe 7473 yang mempunyai 2 buah JK flip-flop

§SFF mengikuti keadaan yang

ditentukan oleh MFF. Suatu transisi hanya dapat terjadi dengan

satu pulsa clock penuh.

JK FF DENGAN PRESET CLEAR

Input PRESET dan CLEAR merupakan 2 masukan JK FF untuk operasi secara asinkron

TIMING DIAGRAM JK FF DENGAN INPUT ASINKRON

APLIKASI JK FF ; PEMBAGI FREKUENSI DAN PEENJAJAH

D (DATA/DELAY FF) TERDETAK

§Merupakan modifikasi dari SR flip-flop

dengan tambahan gerbang pembalik pada masukan R sehinga R merupakan komplemen

dari masukan S. Dapat juga dimodifikasi dari JK FF.

§Pada dasarnya sebuah flip-flop memiliki

dua input, pada FF D input yang dibutuhkan hanyalah 1.

§Dengan modifikasi tambahan pada FF SR

dengan NOT Gate, input D akan mengontrol kondisi set dan reset gate.

T (TOGGLE) FLIP FLOP

§Hanya memerlukan satu input T.

§Bila

input T adalah 1 maka keadaan diubah, bila input T = 0 maka keadaan tetap.

Komentar

Posting Komentar